For most current data sheet and other product information, visit www.burr-brown.com

### FEATURES

- SOCKET FOR THE PCM1801

- EASY CONFIGURATION USING THE ON-BOARD DIP SWITCH

- COMPATIBLE WITH THE DEM-DAI MOTHER BOARD

- POWER SUPPLY, DIGITAL I/O, AND ANALOG INPUT CONNECTORS

- REQUIRES A SINGLE +5V POWER SUPPLY

# DEM-PCM1801 DEM-DAI1801 EVALUATION FIXTURE

### DESCRIPTION

The DEM-PCM1801 is a basic evaluation fixture for the PCM1801 16-bit stereo audio A/D converter. It may be used as part of the customer's prototype system design, or in conjunction with the DEM-DAI mother board to provide a complete evaluation platform for the PCM1801.

#### **ORDERING INFORMATION**

| PART NUMBER                | DESCRIPTION                                                                          |

|----------------------------|--------------------------------------------------------------------------------------|

| DEM-PCM1801<br>DEM-DAI1801 | Basic Evaluation Fixture<br>Includes the DEM-PCM1801 and the DEM-DAI<br>Mother Board |

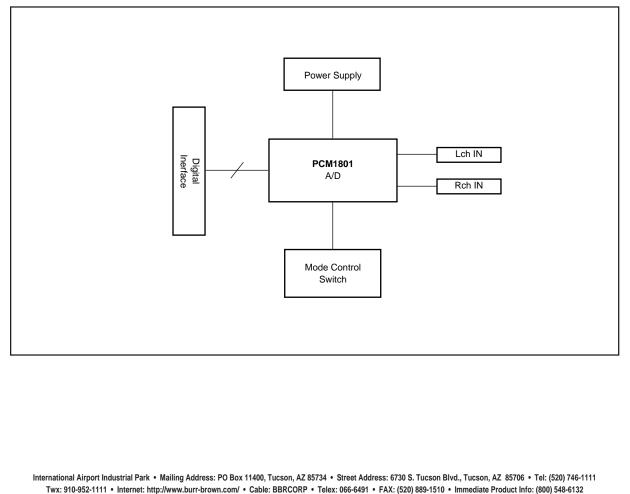

### **BLOCK DIAGRAM**

## HARDWARE DESCRIPTION

#### POWER SUPPLY

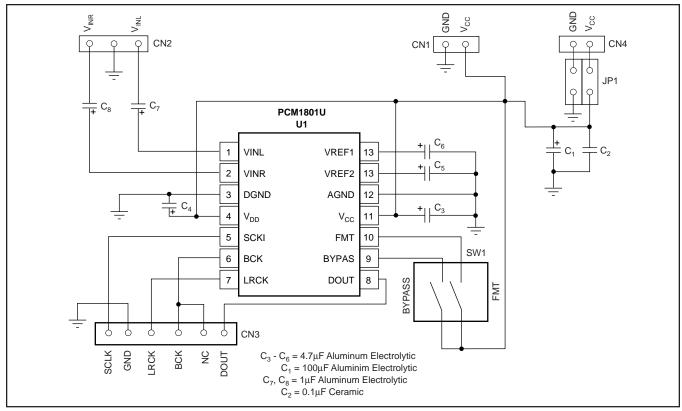

The DEM-PCM1801 requires a single +5V supply. Two connectors are provided for the power supply: CN1 and CN4. For standalone operation, the power supply may be connected to either CN1 or CN4. When using the DEM-PCM1801 in conjunction with the DEM-DAI mother board, connector CN4 is used as the power supply connector.

When using connector CN4, jumpers must be installed at JP1.

The DEM-PCM1801 includes all necessary power supply filter and bypass capacitors. Refer to Figure 1 for connections and component values.

#### ANALOG INPUTS

The PCM1801's left and right analog inputs are available at connector CN2. Both inputs are AC coupled using  $1\mu$ F aluminum electrolytic capacitors. The full scale input signal for the PCM1801 is 2.828Vp-p (or 1Vrms).

#### **DIGITAL INTERFACE**

Connector CN3 provides the interface to the PCM 1801's audio serial port and system clock inputs. The PCM1801 is a Slave device, meaning that all clocks must be provided by an external audio source.

SCLK is the system clock input, which may be 256, 384, or 512 times the sampling frequency ( $f_S$ ). The sampling frequency may be set from 4kHz to 48kHz. LRCK is the left/ right word clock, which operates at the sampling frequency.

BCK is the bit clock, which operates at 32, 48, or 64 times the sampling frequency. DOUT is the audio data output, carrying 16-bit data for both the Left and Right channels.

When used in conjunction with the DEM-DAI mother board, all necessary clocks can be derived from the mother board's crystal oscillator/divider circuitry. The PCM1801's data output (DOUT) may be transmitted over coaxial cable or optical link using the mother board's S/PDIF transmitter circuitry. Refer to the DEM-DAI data sheet for more information regarding mother board use and configuration.

#### **DIP SWITCH**

Switch SW1 is used to configure the PCM1801's audio data format and enable/disable the on-chip digital high-pass filter. The high-pass filter may be used to remove the DC offset generated by the on-chip AFE circuitry. Table I shows the available settings for switch SW1.

| SWITCH | FUNCTION                                 | SETTINGS                                                                       |

|--------|------------------------------------------|--------------------------------------------------------------------------------|

| FMT    | Selects Audio Data Format <sup>(1)</sup> | L = 16-Bit Left-Justified, MSB first<br>H = 16-Bit I <sup>2</sup> S, MSB first |

| BYPASS | Enables or Disables the HPF              | L = HPF Enabled                                                                |

|        |                                          | H = HPF Disabled (or Bypassed)                                                 |

NOTE: (1) Audio data must be in Binary Two's Complement format.

TABLE I. DIP Switch (SW1) Configuration

#### SCHEMATICS

A schematic of the DEM-PCM1801 evaluation fixture is shown in Figure 1.

FIGURE 1. Schematic for the DEM-PCM1801 Evaluation Fixture.

**DEM-PCM1801**

#### PCB LAYOUT

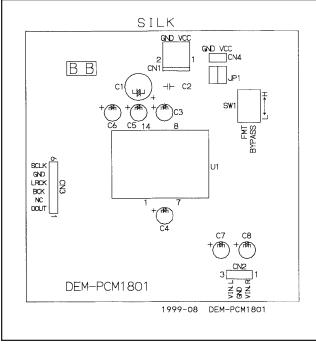

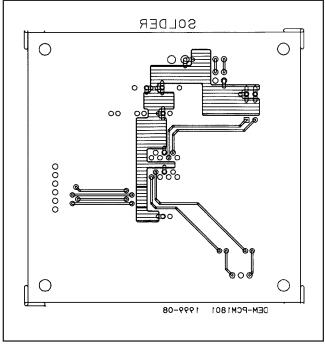

Figures 2 through 4 show the printed circuit board (PCB) plots for the DEM-PCM1801.

Figure 2. Silk Screen (Top Side).

Figure 3. Top Side Layer.

Figure 4. Bottom Side Layer.